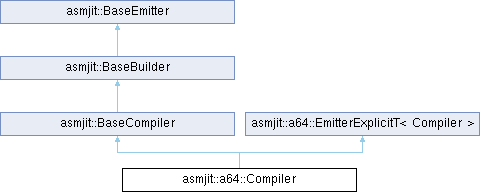

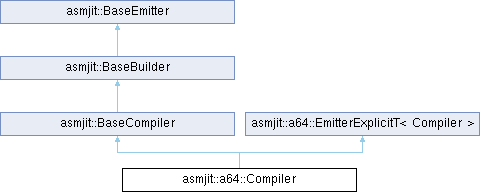

asmjit::a64::Compiler Class Reference [¶]

AArch64 compiler implementation.

AArch64 compiler implementation.

Creates a new general-purpose register with type_id type and optional name passed via args.

Using TypeId is too generic. In general it's recommended to use new_gp32(), new_gp64(), and new_gpz() or new_gp_ptr().

Creates a new vector register with type_id type and optional name passed via args.

Using TypeId is too generic. In general it's recommended to use new_vec128(), new_vec_s(), new_vec_d(), new_vec_q(), ...

Creates a new 32-bit general purpose register mapped to low 32 bits of a full register (on 64-bit targets).

Creates a new 64-bit general purpose register.

Creates a new 32-bit general purpose register.

This is a convenience function alias of new_gp32().

Creates a new 64-bit general purpose register.

This is a convenience function alias of new_gp64().

Creates a new 32-bit or 64-bit general purpose register depending on the target register width.

This is a convenience function, on aarch64 target it always creates a 64-bit general-purpose register.

Creates a new 32-bit or 64-bit general purpose register depending on the target register width.

This is a convenience function, on aarch64 target it always creates a 64-bit general-purpose register.

Creates a new 128-bit vector register.

Creates a new 128-bit vector register that will be used for scalar 32-bit floating point operation.

Creates a new 128-bit vector register that will be used for scalar 64-bit floating point operation.

Creates a new 128-bit vector register that will be used for packed 32-bit floating point operation.

Creates a new 128-bit vector register that will be used for packed 64-bit floating point operation.

Creates a new 32-bit vector register (S).

This may look like an alias of new_vec128_f32x1(), but it's not. This really creates a 32-bit register, which has a type RegType::kVec32, whereas new_vec128_f32x1() creates a register, which has a type RegType::kVec64

Alias of new_vec128_f64x1() that matches aarch64 architecture terminology.

Alias of new_vec128() that matches aarch64 architecture terminology.

Creates a new stack and returns a Mem operand that can be used to address it.

Put data to a constant-pool and get a memory reference to it.

Put a BYTE val to a constant-pool (8 bits).

Put a HWORD val to a constant-pool (16 bits).

Put a WORD val to a constant-pool (32 bits).

Put a DWORD val to a constant-pool (64 bits).

Put a WORD val to a constant-pool.

Put a WORD val to a constant-pool.

Put a DWORD val to a constant-pool.

Put a DWORD val to a constant-pool.

Put a QWORD val to a constant-pool.

Put a QWORD val to a constant-pool.

Put a SP-FP val to a constant-pool.

Put a DP-FP val to a constant-pool.

Force the compiler to not follow the conditional or unconditional jump.

Special pseudo-instruction that can be used to load a memory address into o0 GP register.

At the moment this instruction is only useful to load a stack allocated address into a GP register for further use. It makes very little sense to use it for anything else. The semantics of this instruction is the same as X86 LEA (load effective address) instruction.

Invoke a function call of the given target and signature and store the added node to out.

Creates a new InvokeNode, initializes all the necessary members to match the given function signature, adds the node to the compiler, and stores its pointer to out. The operation is atomic, if anything fails nullptr is stored in out and error code is returned.

This is an overloaded member function, provided for convenience. It differs from the above function only in what argument(s) it accepts.

This is an overloaded member function, provided for convenience. It differs from the above function only in what argument(s) it accepts.

This is an overloaded member function, provided for convenience. It differs from the above function only in what argument(s) it accepts.

This is an overloaded member function, provided for convenience. It differs from the above function only in what argument(s) it accepts.

Return from function.

This doesn't end the function - it just emits a return.

Return from function - one value.

This doesn't end the function - it just emits a return.

Return from function - two values / register pair.

This doesn't end the function - it just emits a return.

Adds a jump to the given target with the provided jump annotation.

Called after the emitter was attached to CodeHolder.

Reimplemented from asmjit::BaseCompiler.

Called after the emitter was detached from CodeHolder.

Reimplemented from asmjit::BaseCompiler.

Called when CodeHolder is reinitialized when the emitter is attached.

Reimplemented from asmjit::BaseCompiler.

Finalizes this emitter.

Materializes the content of the emitter by serializing it to the attached CodeHolder through an architecture specific BaseAssembler. This function won't do anything if the emitter inherits from BaseAssembler as assemblers emit directly to a CodeBuffer held by CodeHolder. However, if this is an emitter that inherits from BaseBuilder or BaseCompiler then these emitters need the materialization phase as they store their content in a representation not visible to CodeHolder.

Reimplemented from asmjit::BaseEmitter.