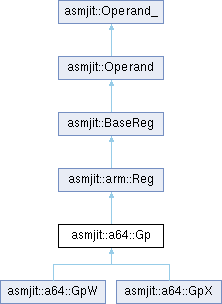

asmjit::a64::Gp Class Reference [¶]

General purpose register (AArch64).

General purpose register (AArch64).

Special register id.

Default constructor that only setups basics.

Makes a copy of the other register having id set to id

Creates a register based on signature and id.

Creates a completely uninitialized Gp register operand (garbage).

Creates a new register from register type and id.

Copy assignment operator - copies the content of other to this register.

Creates a new 32-bit low general purpose register (W) having the given register id reg_id.

Creates a new 64-bit low general purpose register (X) having the given register id reg_id.

Creates a new 32-bit low general purpose register (W) having the given register id reg_id.

Creates a new 64-bit low general purpose register (X) having the given register id reg_id.

Test whether this register is ZR register.

Test whether this register is SP register.

Clones and casts this register to a 32-bit (W) register.

Clones and casts this register to a 64-bit (X) register.