AsmJit Project

Low-Latency Machine Code Generation

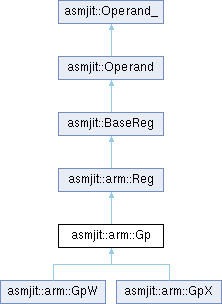

General purpose register (ARM).

Public Types inherited from asmjit::BaseReg

Public Types inherited from asmjit::BaseReg Public Types inherited from asmjit::Operand_

Public Types inherited from asmjit::Operand_ Public Member Functions inherited from asmjit::arm::Reg

Public Member Functions inherited from asmjit::arm::Reg Public Member Functions inherited from asmjit::BaseReg

Public Member Functions inherited from asmjit::BaseReg Public Member Functions inherited from asmjit::Operand

Public Member Functions inherited from asmjit::Operand Public Member Functions inherited from asmjit::Operand_

Public Member Functions inherited from asmjit::Operand_ Public Attributes inherited from asmjit::Operand_

Public Attributes inherited from asmjit::Operand_ Static Public Member Functions inherited from asmjit::arm::Reg

Static Public Member Functions inherited from asmjit::arm::Reg Static Public Member Functions inherited from asmjit::BaseReg

Static Public Member Functions inherited from asmjit::BaseReg Static Public Member Functions inherited from asmjit::Operand_

Static Public Member Functions inherited from asmjit::Operand_Special register id.