AsmJit

Low-Latency Machine Code Generation

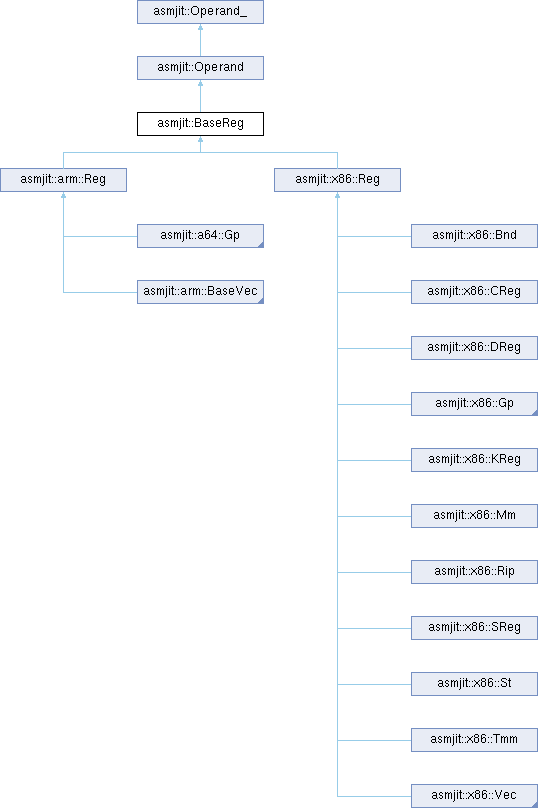

Physical or virtual register operand (base).

Public Member Functions inherited from asmjit::Operand

Public Member Functions inherited from asmjit::Operand Public Member Functions inherited from asmjit::Operand_

Public Member Functions inherited from asmjit::Operand_ Public Attributes inherited from asmjit::Operand_

Public Attributes inherited from asmjit::Operand_ Public Types inherited from asmjit::Operand_

Public Types inherited from asmjit::Operand_Creates a dummy register operand.

Creates a new register operand which is the same as other .

Creates a new register operand compatible with other, but with a different id.

Creates a register initialized to the given signature and id.

Returns base signature of the register associated with each register type.

Base signature only contains the operand type, register type, register group, and register size. It doesn't contain element type, predicate, or other architecture-specific data. Base signature is a signature that is provided by architecture-specific RegTraits, like x86::RegTraits.

Tests whether the operand's base signature matches the given signature sign.

Tests whether the operand's base signature matches the given signature sign.

Tests whether the operand's base signature matches the base signature of the other operand.

Tests whether this register is the same as other.

This is just an optimization. Registers by default only use the first 8 bytes of Operand data, so this method takes advantage of this knowledge and only compares these 8 bytes. If both operands were created correctly both equals() and isSame() should give the same answer, however, if any of these two contains garbage or other metadata in the upper 8 bytes then isSame() may return true in cases in which equals() returns false.

Tests whether the register is valid (either virtual or physical).

Tests whether this is a physical register.

Tests whether this is a virtual register.

Tests whether the register type matches type - same as isReg(type), provided for convenience.

Tests whether the register group matches group.

Tests whether the register is a general purpose register (any size).

Tests whether the register is a vector register of any size.

Tests whether the register is a mask register of any size.

Same as isType(), provided for convenience.

Tests whether the register type matches type and register id matches id.

Tests whether the register specifies a size (i.e. the size is not zero).

Tests whether the register size matches size s.

Returns the size of the register in bytes.

If the register size depends on architecture (like x86::CReg and x86::DReg) the size returned should be the greatest possible (so it should return 64-bit size in such case).

Returns operation predicate of the register (ARM/AArch64).

The meaning depends on architecture, for example on ARM hardware this describes arm::ShiftOp of the register.

Sets operation predicate of the register to predicate (ARM/AArch64).

The meaning depends on architecture, for example on ARM hardware this describes arm::ShiftOp of the register.

Resets shift operation type of the register to the default value (ARM/AArch64).

Casts this register to RegT by also changing its signature.

cloneAs() can lead to hard-to-debug errors. Casts this register to other by also changing its signature.

cloneAs() can lead to hard-to-debug errors. Sets the register id to id.

Sets a 32-bit operand signature based on traits of RegT.

Sets the register signature and id.

Tests whether the op operand is a general purpose register.

Tests whether the op operand is a vector register.

Tests whether the op is a general purpose register of the given id.

Tests whether the op is a vector register of the given id.

Tests whether the operand is a register (OperandType::kReg).

Tests whether the operand is a register matching the given register type.

Tests whether the operand is a register of the provided register group regGroup.

Tests whether the operand is register and of register type regType and regId.

Tests whether the operand is register and of register group regGroup and regId.

None or any register (mostly internal).